# Architecture Matters: Choosing the Right SoC FPGA for Your Application

**White Paper**

101 Innovation Drive San Jose, CA 95134 www.altera.com

WP-01202-1.0

Document publication date: November 2013

© 2013 Altera Corporation. All rights reserved. ALTERA, ARRIA, CYCLONE, ENPIRION, HARDCOPY, MAX, MEGACORE, NIOS, QUARTUS and STRATIX are Reg. U.S. Pat. & Tm. Off. and/or trademarks of Altera Corporation in the U.S. and other countries. All other trademarks and service marks are the property of their respective holders as described at www.altera.com/common/legal.html. Altera warrants performance of its semiconductor products to current specifications in accordance with Altera's standard warranty, but reserves the right to make changes to any products and services at any time without notice. Altera assumes no responsibility or liability arising out of the application or use of any information, product, or service described herein except as expressly agreed to in writing by Altera. Altera customers are advised to obtain the latest version of device specifications before relying on any published information and before placing orders for products or services.

| Introduction                                                                 | 1–1  |

|------------------------------------------------------------------------------|------|

| SoC FPGAs Available Today                                                    | 1–1  |

| Benefits Over Two-chip Processor and FPGA Applications                       |      |

| Benefits Over ASIC-Based Processors                                          | 1–3  |

| Benefits Over Other Processors or Microcontrollers                           | 1–4  |

| How to Choose the Right SoC FPGA for a Specific Application                  |      |

| System Performance                                                           | 1–4  |

| Importance of the L3 Interconnect: Central Switch for Maximum Performance    | 1–5  |

| Processor-to-FPGA Interconnect: Ensuring the Benefit of an Integrated Device |      |

| DDR Memory Controller Performance                                            |      |

| FPGA Connection to Processor's DDR Memory Controller                         | 1–11 |

| Hardware Acceleration and Cache Coherency                                    | 1–13 |

| Additional Memory Controllers Improve Maximum System Performance             |      |

| System Reliability and Flexibility                                           |      |

| Protecting Memory Contents with ECC                                          |      |

| Memory Protection for Shared Memory                                          |      |

| Watchdog Reset and Its Effect on FPGA Logic                                  |      |

| Fail-Safe Booting and Configuration                                          |      |

| Flexibility                                                                  |      |

| Multiple Options for Processor Boot and FPGA Configuration                   |      |

| Multiple Boot Images                                                         |      |

| On-Chip FPGA Interfaces                                                      | 1–21 |

| Common Footprint Density/Transceiver/Feature Migration                       |      |

| System Cost                                                                  |      |

| Integrated Functionality                                                     |      |

| High-Speed Transceivers                                                      |      |

| Power Supply Cost                                                            |      |

| Power                                                                        |      |

| Power Savings via Integration                                                |      |

| Power-Saving Modes                                                           |      |

| Power-On/Off Sequencing Requirements                                         |      |

| Future Roadmap                                                               | 1–27 |

| Altera's Three-Generation Processor Roadmap                                  |      |

| The Foundation: Silicon Process Technology                                   |      |

| FinFET Technology                                                            |      |

| Tools Roadmap                                                                |      |

| Development Tools                                                            |      |

| Development Tool Challenges                                                  |      |

| ARM Compatibility a Given; FPGA Implementation a Difference                  |      |

| Whole-Chip Debugging                                                         |      |

| FPGA-Adaptive Debugging                                                      |      |

| Single Debug Cable for ARM and FPGA Development                              |      |

| Cross-Triggering Between Hardware and Software                               |      |

| Tracking and Monitoring Hardware and Software Events                         |      |

| Profiling CPUs and FPGA                                                      |      |

| Multicore Debugging                                                          |      |

| Standard Tools and Flows                                                     |      |

| ARM DS-5 Altera Edition Toolkit                                              |      |

| Development Tools Summary                                                    |      |

| *                                                                            |      |

| Conclusion                | 1–38 |

|---------------------------|------|

| Further Information       | 1–39 |

| Acknowledgements          | 1–39 |

| Document Revision History | 1–39 |

## Architecture Matters: Choosing the Right SoC FPGA for Your Application

WP-01202-1.0

White Paper

This white paper presents and analyzes various metrics to help system architects, engineers and managers decide if SoC FPGAs are a fit for their application and, if so, which vendor's devices may be best suited. Key aspects of this paper are also highlighted in an online video series, A Look Inside: SoC FPGAs.

## Introduction

SoC FPGA devices integrate both processor and FPGA architectures into a single device. Melding the two technologies provides a variety of benefits including higher integration, lower power, smaller board size, and higher bandwidth communication between the processor and FPGA. Best-in-class devices exploit the unique advantages of a merged processor and FPGA system while retaining the benefits of a stand-alone processor and FPGA approach.

## SoC FPGAs Available Today

At present, there are primarily three SoC FPGAs on the market, as shown in Table 1. The processors in these devices are fully dedicated, "hardened" processor subsystems, (not a soft intellectual property (IP) core implemented in the FPGA fabric). All three of these device families employ a full-featured ARM<sup>®</sup> processor with a complete memory hierarchy and dedicated peripherals that largely boot, run, and act like any "normal" ARM processor.

The Microsemi SmartFusion2 SoC FPGAs are based around the ARM Cortex<sup>TM</sup>-M3 embedded processor, primarily targeting microcontroller applications. The Altera SoC FPGA and Xilinx Zynq-7000 devices use a dual-core ARM Cortex-A9 application processor. In addition to the processor, an SoC FPGA includes a rich set of peripherals, on-chip memory, an FPGA-style logic array, and plentiful I/O. Refer to Table 1.

|                          | Altera SoC FPGAs                                  | Xilinx Zynq-7000 EPP  | Microsemi SmartFusion2 |

|--------------------------|---------------------------------------------------|-----------------------|------------------------|

| Processor                | ARM Cortex-A9                                     | ARM Cortex-A9         | ARM Cortex-M3          |

| Processor Class          | Application processor                             | Application processor | Microcontroller        |

| Single or Dual Core      | Single or Dual                                    | Dual                  | Single                 |

| Processor Max. Frequency | 1.05 GHz                                          | 1.0 GHz               | 166 MHz                |

| L1 Cache                 | Data: 32 KB                                       | Data: 32 KB           | No data cache          |

|                          | Instruction: 32 KB                                | Instruction: 32 KB    | Instruction: 8 KB      |

| L2 Cache                 | Unified: 512 KB, with error correction code (ECC) | Unified: 512 KB       | Not available          |

101 Innovation Drive San Jose, CA 95134 www.altera.com © 2013 Altera Corporation. All rights reserved. ALTERA, ARRIA, CYCLONE, ENPIRION, HARDCOPY, MAX, MEGACORE, NIOS, QUARTUS and STRATIX words and logos are trademarks of Altera Corporation and registered in the U.S. Patent and Trademark Office and in other countries. All other words and logos identified as trademarks or service marks are the property of their respective holders as described at www.altera.com/common/legal.html. Altera warrants performance of its semiconductor products to current specifications in accordance with Altera's standard warranty, but reserves the right to make changes to any products and services at any time without notice. Altera assumes no responsibility or liability arising out of the application or use of any information, product, or service described herein except as expressly agreed to in writing by Altera. Altera customers are advised to obtain the latest version of device specifications before relying on any published information and before placing orders for products or services.

|                                                   | Altera SoC FPGAs                                                                                                                                                                                                                                                                                                                                                                                                        | Xilinx Zynq-7000 EPP                                                                                                                                                                                                                                                                                                                                                                                                                        | Microsemi SmartFusion2                                                                                                                                                                                                     |

|---------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Memory Management Unit<br>(MMU)                   | Yes                                                                                                                                                                                                                                                                                                                                                                                                                     | Yes                                                                                                                                                                                                                                                                                                                                                                                                                                         | Yes                                                                                                                                                                                                                        |

| Floating-Point<br>Unit/NEON™ Multimedia<br>Engine | Yes                                                                                                                                                                                                                                                                                                                                                                                                                     | Yes                                                                                                                                                                                                                                                                                                                                                                                                                                         | Not available                                                                                                                                                                                                              |

| Acceleration Coherency<br>Port (ACP)              | Yes                                                                                                                                                                                                                                                                                                                                                                                                                     | Yes                                                                                                                                                                                                                                                                                                                                                                                                                                         | Not available                                                                                                                                                                                                              |

| Interrupt Controller                              | Generic (GIC)                                                                                                                                                                                                                                                                                                                                                                                                           | Generic (GIC)                                                                                                                                                                                                                                                                                                                                                                                                                               | Nested, vectored (NVIC)                                                                                                                                                                                                    |

| On-Chip Processor RAM                             | 64 KB, with ECC                                                                                                                                                                                                                                                                                                                                                                                                         | 256 KB, no ECC                                                                                                                                                                                                                                                                                                                                                                                                                              | 64 KB, no ECC                                                                                                                                                                                                              |

| Direct Memory Access<br>Controller                | 8-channel ARM DMA330<br>32 peripheral requests (FPGA<br>+ hard processor system                                                                                                                                                                                                                                                                                                                                         | 8-channel ARM DMA330<br>4 peripheral requests (FPGA<br>only)                                                                                                                                                                                                                                                                                                                                                                                | 1-channel HPDMA<br>4 requests                                                                                                                                                                                              |

| External Memory<br>Controller                     | Yes                                                                                                                                                                                                                                                                                                                                                                                                                     | Yes                                                                                                                                                                                                                                                                                                                                                                                                                                         | Yes                                                                                                                                                                                                                        |

| Memory Types Supported                            | LPDDR2, DDR2, DDR3L,<br>DDR3                                                                                                                                                                                                                                                                                                                                                                                            | LPDDR2, DDR2, DDR3L,<br>DDR3                                                                                                                                                                                                                                                                                                                                                                                                                | LPDDR, DDR2, DDR3                                                                                                                                                                                                          |

| External Memory ECC                               | 16 bit, 32 bit                                                                                                                                                                                                                                                                                                                                                                                                          | 16 bit                                                                                                                                                                                                                                                                                                                                                                                                                                      | 8 bit, 16 bit, 32 bit                                                                                                                                                                                                      |

| External Memory Bus<br>Max. Frequency             | 400 MHz (Cyclone® V SoC),<br>533 MHz (Arria® V SoC)                                                                                                                                                                                                                                                                                                                                                                     | 533 MHz                                                                                                                                                                                                                                                                                                                                                                                                                                     | 333 MHz                                                                                                                                                                                                                    |

| Processor Peripherals                             | 1x quad SPI controller with 4<br>chip selects<br>1x NAND controller (single-<br>and multilevel cell - MLC or<br>SLC)<br>2x 10/100/1G Ethernet<br>controller<br>2x USB 2.0 On-the-Go (OTG)<br>controller<br>1x SD/MMC/SDIO controller<br>2x UART<br>4x I <sup>2</sup> C controller<br>2x CAN controller<br>2x SPI master, 2x SPI slave<br>controller<br>4x 32 bit general-purpose<br>timers<br>2x 32 bit watchdog timers | 1x quad SPI or dual quad SPI<br>controller with 2 chip selects<br>1x static memory controller<br>(NAND-SLC, NOR, or<br>SSRAM)<br>2x 10/100/1G Ethernet<br>controller<br>2x USB 2.0 OTG controller<br>2x USB 2.0 OTG controller<br>2x SD/SDIO controller<br>2x UART<br>2x I <sup>2</sup> C controller<br>2x CAN controller<br>2x SPI controllers (master or<br>slave)<br>2x 16 bit triple-mode<br>timer/counters<br>1x 24 bit watchdog timer | 1x 10/100/1G Ethernet<br>controller<br>2x USB 2.0 OTG controller<br>2x UART<br>2x I <sup>2</sup> C controller<br>1x CAN controller<br>2x SPI<br>2x general-purpose timers<br>1x watchdog timer<br>1x real-time clock (RTC) |

| FPGA Fabric                                       | Cyclone V, Arria V                                                                                                                                                                                                                                                                                                                                                                                                      | Artix-7, Kintex-7                                                                                                                                                                                                                                                                                                                                                                                                                           | Fusion2                                                                                                                                                                                                                    |

| FPGA Logic Density Range                          | 25 K to 462 K LE                                                                                                                                                                                                                                                                                                                                                                                                        | 28 K to 444 K LC                                                                                                                                                                                                                                                                                                                                                                                                                            | 6 K to 146 K LE                                                                                                                                                                                                            |

| Hardened Memory<br>Controllers in FPGA            | Up to 3, with ECC                                                                                                                                                                                                                                                                                                                                                                                                       | Not available                                                                                                                                                                                                                                                                                                                                                                                                                               | Not available                                                                                                                                                                                                              |

| High-speed Transceivers                           | Available at all densities                                                                                                                                                                                                                                                                                                                                                                                              | Higher-density devices only                                                                                                                                                                                                                                                                                                                                                                                                                 | Higher-density devices only                                                                                                                                                                                                |

#### Table 1. Commercially-Available SoC FPGAs (Part 2 of 3)

Table 1. Commercially-Available SoC FPGAs (Part 3 of 3)

|                              | Altera SoC FPGAs                                  | Xilinx Zynq-7000 EPP                                       | Microsemi SmartFusion2                |

|------------------------------|---------------------------------------------------|------------------------------------------------------------|---------------------------------------|

| Analog Mixed Signal<br>(AMS) | Not available                                     | 2 x 12-bit, 1 MSPS analog-to-<br>digital converters (ADCs) | Not available                         |

| Boot Sequence                | Processor first, FPGA first, or both simultaneous | Processor first                                            | Processor boot, FPGA non-<br>volatile |

Does an SoC FPGA make sense for a next-generation system design? The following three questions may help a system designer, architect, or hardware manager make that determination:

- Does the existing design use an FPGA and a separate microprocessor?

- Does the current generation use a proprietary ASIC that includes a microprocessor?

- Is a microprocessor being used today, but would benefit from a peripheral set more tailored to the application?

## **Benefits Over Two-chip Processor and FPGA Applications**

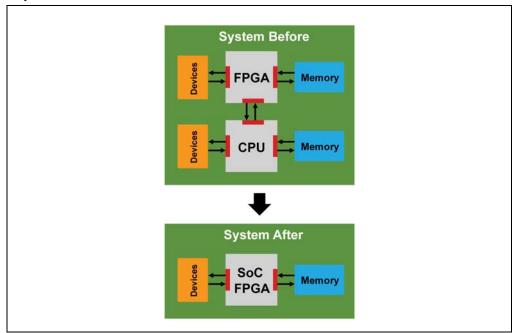

For designs that already use an FPGA and a separate microprocessor, these devices should definitely be considered.

The SoC FPGA likely provides at least comparable, and likely superior, functionality and performance, but at a lower board space, lower power, and lower system cost by as much as 50% less. Integrating these technologies on the same piece of silicon eliminates the cost of one of the plastic packages, and one device saves a lot of board space compared with two. If both the CPU and FPGA in the design use separate external memories, it may also be possible to consolidate both into one memory device, saving even more system cost, board space, and power. Because the signals between the processor and the FPGA now reside on the same silicon, communication between the two consumes substantially less power compared to using separate chips. Plus, thanks to thousands of internal connections between the processor and the FPGA, an integrated solution has substantially higher bandwidth and lower latency compared to a two-chip solution.

## **Benefits Over ASIC-Based Processors**

What if the current design uses a proprietary ASIC that includes a microprocessor? Most design teams that currently use ASIC technology have probably already investigated FPGAs at some point and likely use them during the prototyping or emulation phase. For many ASIC designers, the previous lack of an ARM processor has been a barrier to using FPGA technology for full production. This new breed of SoC FPGAs delivers a fully-functional, fully-compatible, high-performance dual-core ARM Cortex-A9 processor running up to 1 GHz with today's 28 nm process technology, eliminating that barrier.

Because SoC FPGAs leverage programmable logic technology, programmable designs benefit from all the traditional FPGA advantages over standard ASIC technology, such as:

• *No expensive mask charges or minimum purchase requirements*—Build and ship a single, cost-effective SoC FPGA solution or millions

- Faster time to market—No manufacturing lead times; devices available off-the-shelf at major electronics distributors

- Lower risk—Reprogram the SoC FPGA at any time, even after the product has shipped. Supports in-field updates and upgrades

- Adapt to changing markets requirements and emerging standards

- No additional licensing or royalty payments for the embedded processor, highspeed transceivers, or other advanced system technology

#### **Benefits Over Other Processors or Microcontrollers**

In the final scenario, systems that typically use stand-alone microprocessors or highend microcontrollers but not FPGAs may still benefit from these new SoC FPGAs. Why? Many designers research the available off-the-shelf processors and often settle for a device that only approximately fits the application—the selected processor is missing an Ethernet port, USB channels, interrupt lines, and so on. The power of these SoC FPGAs is that a custom ARM microprocessor derivative can be created instantly, right on the desktop. System designs that have been forced to accept compromises due to the lack of off-the-shelf processor derivatives can now be customized to fit the application. Hence, the design can be differentiated both in hardware and software, making it more difficult for competitors to copy or emulate.

#### How to Choose the Right SoC FPGA for a Specific Application

At first glance, the programmable SoC offerings in Table 1 from various vendors might appear similar. They all integrate an ARM processor, various peripherals, and an FPGA into a single device. In practice, however, it is critical to closely evaluate these offerings, and look deeper than the data sheet. The underlying architecture and its implications must be evaluated relative to a specific application. The SoC FPGA architecture matters. Closer examination and consideration reveals many significant differences at an architectural level.

So how does a designer choose? This white paper presents design considerations and engineering trade-off decisions for choosing the best programmable SoC for an application. The selection criteria centers on these six areas:

- System performance

- System reliability and flexibility

- System cost

- Power consumption

- Future roadmap

- Development tools

## **System Performance**

Ultimately, two areas of the SoC FPGA architecture dominate the efficient movement of data between the different elements:

- The interconnect

- Memory bandwidth, both on-chip and off

## Importance of the L3 Interconnect: Central Switch for Maximum Performance

The first item to consider in an SoC architecture is the Level-3 (L3) interconnect. The L3 interconnect, named for being the next level beyond the L1 and L2 caches for data transfers, routes data between the memory, FPGA fabric, processor, and peripherals. Table 2 shows the SoC FPGA vendors feature comparison for the L3 system interconnect.

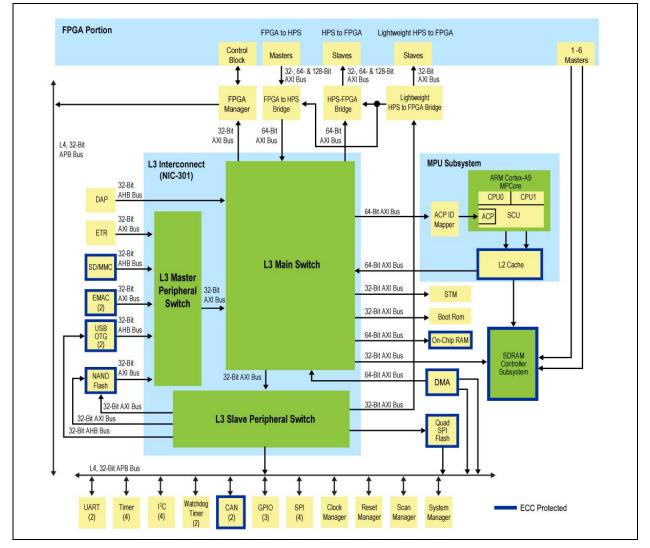

Altera SoC FPGAs provide an L3 system interconnect comprised of three switches— L3 main switch, L3 master peripheral switch, L3 slave peripheral switch implemented using ARM's AMBA<sup>®</sup> NIC-301 Network Interconnect infrastructure as shown in Figure 1.

Altera SoCs use a reduced-hierarchy bus to minimize latency with a non-blocking switch architecture. The interconnect was designed to support multiple, simultaneous transactions from multiple masters with sufficient bandwidth such that each master can run without stalling ("non-blocking"). For arbitration, each master can be assigned its own priority level to guide bus arbitration. Masters with equal priority are arbitrated using a least recently used (LRU) algorithm.

Alternative SoC FPGA architectures may use a multi-level hierarchy that may introduce latency. Distributed arbitration is analogous to having multiple traffic cops. This approach necessitates the use of a central quality of service (QoS) module to ensure that no master gets stuck. Distributed arbitration also presents tuning challenges and may conflict with DDR memory controller port arbitration.

Table 2. L3 System Interconnect Feature Comparison in SoC FPGA Devices

| Function/Feature | Altera SoC FPGA                                                               | Vendor B                             |

|------------------|-------------------------------------------------------------------------------|--------------------------------------|

| Infrastructure   | ARM AMBA NIC-301                                                              | ARM AMBA NIC-301                     |

| Bus Hierarchy    | Reduced hierarchy                                                             | Multi-level                          |

| Arbitration      | Programmable priority for each master.<br>LRU for requests of equal priority. | Distributed, regulated by QoS block. |

## Processor-to-FPGA Interconnect: Ensuring the Benefit of an Integrated Device

One of the significant promises of the SoC FPGA architecture is the tight, on-chip coupling of the processor and FPGA. To realize this performance promise, it is critical that the processor-to-FPGA interconnect be constructed with sufficient bandwidth (width and speed) and of the right types so as not to become the bottleneck of system data transfers.

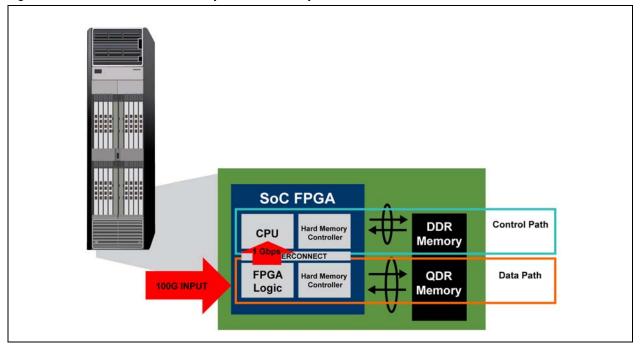

To illustrate this point, imagine that a communication line card application, shown in Figure 2, needs to process 100 gigabits per second of network data. The FPGA can nimbly handle the incoming data. However, even if the processor only touches 1% of the traffic, a substantial 1 Gbps of data must flow across the interconnect between the FPGA logic and the processor. Fortunately, SoC FPGAs available today support up to 125 Gbps or more of throughput between the FPGA logic and the processor, substantially more than enough for this type of application.

Figure 2. Communication Line Card Requires Over 100 Gbps Interconnect Bandwidth Between FPGA and Processor

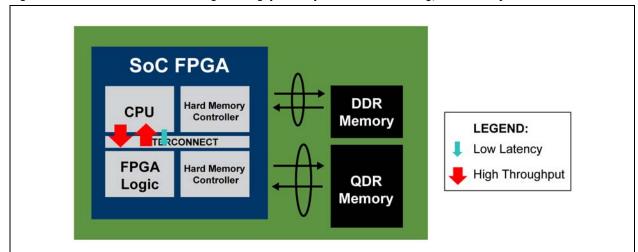

In terms of structure, in some SoC FPGA devices the datapath and control path compete for bandwidth. The processor may need to set up and configure accesses to hardware accelerators in the FPGA logic. If these control transactions compete with data traffic, they may block the high-throughput data traffic, halting the continuous processing of incoming data. Similarly, control signals may be delayed by high-bandwidth data traffic, adding to control latency.

To prevent this, the Altera SoC FPGAs feature a second, low-latency, nonblocking,"lightweight" interconnect bridge. The processor accesses control registers in the FPGA via this simple 32 bit ARM Advanced eXtensible Interface (AXI<sup>TM</sup>) interface, without blocking or affecting the high-throughput data flow, shown in blue in Figure 3. Meanwhile, high-bandwidth data connections between the processor and FPGA support 32, 64, or 128 bit wide transactions, shown in red in Figure 3. Table 3 shows the configuration of both sets of datapaths.

Figure 3. Altera SoC FPGAs Feature High-Throughput Datapath and Non-Blocking, Low-Latency Control Path

Table 3. Processor-to-FPGA System Interconnect Features in SoC FPGAs

| Function/Feature                                                               | Altera SoC FPGA                    | Vendor B                                      |

|--------------------------------------------------------------------------------|------------------------------------|-----------------------------------------------|

| High Pandwidth Dragogor/EDCA Interconnect                                      | 1x 32/64/128 bit AXI<br>(CPU→FPGA) | 2x 32 bit AXI<br>(CPU-→FPGA)                  |

| High-Bandwidth Processor/FPGA Interconnect                                     | 1x 32/64/128 bit AXI<br>(FPGA→CPU) | 2x 32 bit AXI<br>(FPGA-→CPU)                  |

| Low-Latency Processor/FPGA Interconnect                                        | 1x 32 bit AXI<br>(CPU→FPGA)        | Must utilize one of the high-bandwidth busses |

| Total Processor/FPGA Interconnect Maximum Theoretical Bandwidth <sup>(1)</sup> | 10.8 GB/s                          | 4.8 GB/s                                      |

| Processor/FPGA Interconnect Data Width                                         | x32, x64, or x128                  | Fixed x32                                     |

| Processor/FPGA Transaction Buffers                                             | 16 writes + ECC                    | 8 writes                                      |

| FIDLESSOI/FFGA Hansaction bullers                                              | 16 reads + ECC                     | 8 reads                                       |

Note:

(1) Assumes 150 MHz interconnect bus speed. Theoretical maximum is bus speed times data width. Actual realized bandwidth will be lower due to protocol and buffering overhead.

## **DDR Memory Controller Performance**

When selecting DDR DRAM for a design, one would typically assume that the memory speed would dominate the realized performance (see Table 4). However, other factors in terms of how intelligent the memory data transfers are prioritized, scheduled, and processed can have significant impact on overall memory performance.

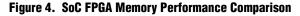

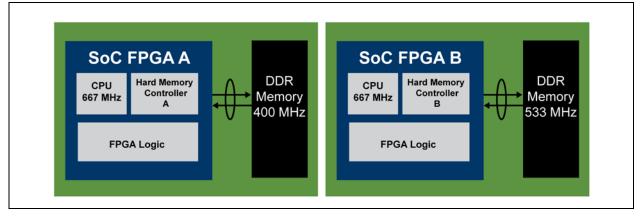

To illustrate this effect, consider two SoC FPGA devices with different memory bus speeds as shown in Figure 4. Both have a dual-core ARM Cortex-A9 processor running at the same frequency of 667 MHz. However, one device has an external memory operating at 400 MHz, while the other uses an external memory running at 533 MHz. At first glance, one would expect the system with 533 MHz memory to exhibit 33% higher performance due to the higher memory performance. However, advances in the memory controller architecture produce some noticeably different results.

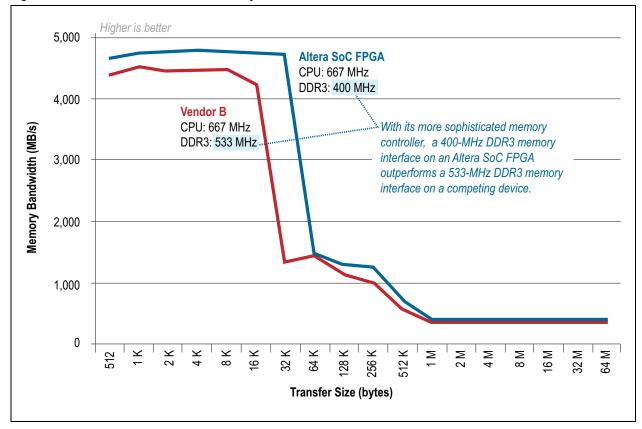

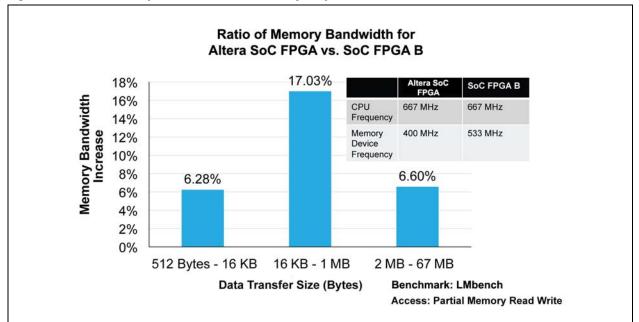

Figure 5 provides the results of a system performance benchmark called LMbench. Altera selected LMbench as it is an industry-standard benchmark (www.bitmover.com/lmbench) known for exercising the memory system performance. The partial read/write case illustrates transfers of a typical embedded application using LMbench version 3.

The bandwidth observed decreases in stages as the data size moves from the L1 cache to the L2 cache to external memory.

Figure 6. LMbench Memory Bandwidth Difference Grouped by Data Transfer Size

Across the full range of small, medium, and large memory accesses, shown in Figure 6, the SoC FPGA with the more advanced memory controller, the Altera SoC FPGA, extracts up to 17% more memory bandwidth despite a slower memory operating frequency.

These results demonstrate that when comparing SoC FPGAs, it is important to check the measured memory system performance, not just the memory bus specifications. This is another example of where architecture matters. Modern memory controllers employ sophisticated algorithms to maximize efficiency from system memory. These algorithms extract maximum bandwidth by managing transaction priority, reordering command and data, and scheduling pending transactions using sophisticated algorithms like deficit weight round robin. Additional performance comes by customizing the memory controller via software to best fit the system's custom data profile, set priorities, assign ports or transaction channels, and even tweak the share of bandwidth between them. A better memory controller not only extracts more bandwidth from system memory, but also may enable the memory to run at a lower frequency and thereby saving power.

**Table 4. External Memory Controller Support Comparison**

| Function/Feature                                            | Altera SoC FPGA                                   | Vendor B                     | Vendor C                                         |

|-------------------------------------------------------------|---------------------------------------------------|------------------------------|--------------------------------------------------|

| Hardened External Memory<br>Controller for Processor System | Yes                                               | Yes                          | Yes                                              |

| Maximum Supported Address Space                             | 4G                                                | 1G                           | 4G                                               |

| Memory Types Supported                                      | LPDDR2, DDR2, DDR3L,<br>DDR3                      | LPDDR2, DDR2, DDR3L,<br>DDR3 | LPDDR, DDR2, DDR3                                |

| Data Width Configuration Modes                              | x8<br>x16<br>x16+ECC<br>x32<br>x32+ECC            | x16<br>x16+ECC<br>x32        | x8<br>x8+ECC<br>x16<br>x16+ECC<br>x32<br>x32+ECC |

| Integrated ECC Support                                      | 16 bit, 32 bit                                    | 16 bit                       | 8 bit, 16 bit, 32 bit                            |

| External Memory Bus Maximum<br>Frequency                    | 400 MHz (Cyclone V SoC),<br>533 MHz (Arria V SoC) | 533MHz                       | 333 MHz                                          |

## FPGA Connection to Processor's DDR Memory Controller

To save cost in SoC FPGA applications, functions built in the FPGA section can optionally access system main memory through the processor's DDR memory controller. However, sharing the processor's memory controller could potentially limit the performance of either the processor or the FPGA. Consequently, the connection from the FPGA to the processor's memory controller must be optimized for bandwidth.

As shown in Table 5, both the Altera SoC FPGAs and those from Vendor B both have 256 total bits out of the FPGA headed toward the processor's memory controller. In Vendor B's device, two of the four 64 bit ports are switched down to the memory controller while two of the four 64 bit ports are switched to the on-chip memory (OCM). In Altera SoC FPGAs, all lines of the 256 bit port are connected directly to the processor memory controller and can be configured with to up to six independent

command/response ports, four read ports, or four write ports. Each port sharing the 256 bit interface can potentially support different bus protocols, different data widths, and different configuration. For example on the Altera SoC FPGA, the FPGA interface to the processor's DDR memory controller simultaneously supports a 128 bit Avalon<sup>®</sup> Memory-Mapped interface and two 64 bit AXI ports. At its maximum interface clock rate, the Altera FPGA-to-DDR memory interface supports up to 9,600 MB/sec peak bandwidth.

This extra bandwidth is a result of the direct connection between the FPGA interface and the processor's memory controller, unencumbered by intervening switches or interconnect layers. The direct connection supplies every memory port with the maximum possible bandwidth and maximum flexibility for prioritizing those transactions. In contrast, the four ports on Vendor B's interface are multiplexed down to two ports on the processor's memory controller, which reduces maximum bandwidth.

These FPGA interfaces to the processor's memory controller also support relative prioritization of traffic. The Altera SoC FPGAs offer eight absolute prioritization levels to custom-tailor communication within the device. Transactions from the FPGA can be dynamically and individually prioritized. Vendor B's SoC FPGAs offer two absolute prioritization levels.

| <b>Function/Feature</b>                                                  | Altera SoC FPGA                                           | Vendor B                                                                                         |

|--------------------------------------------------------------------------|-----------------------------------------------------------|--------------------------------------------------------------------------------------------------|

| FPGA-to-DDR Memory                                                       | 256 bit, AXI/Avalon-MM interface                          | 4x 64 bit AXI                                                                                    |

| Interconnect Path                                                        | (FPGA→DRAM)                                               | (FPGA→DRAM and on-chip RAM)                                                                      |

| Individual Port Size Options                                             | 8/16/32/64/256 bit                                        | 32/64 bit                                                                                        |

| Maximum FPGA to<br>Interconnect Ports                                    | 6 command/response ports<br>4 read ports<br>4 write ports | 4 x64 read ports<br>4 x64 write ports                                                            |

| Maximum Interconnect to<br>Processor DDR Hard Memory<br>Controller Ports | 6 command/response ports<br>4 read ports<br>4 write ports | 2 x64 read port<br>2 x64 write port<br>(multiplexed down from four ports)                        |

| Connection                                                               | Direct                                                    | Switched (four FPGA ports multiplexed<br>down to two DDR memory ports in memory<br>interconnect) |

| FIFO Size                                                                | 16x256 = 512 B + ECC                                      | 128x64 = 1 KB                                                                                    |

| Relative Traffic Prioritization                                          | Yes                                                       | Yes                                                                                              |

| Absolute Prioritization Levels                                           | 8                                                         | 2                                                                                                |

| Maximum Ports for AXI<br>Exclusive Memory Sharing                        | Across all ports, all IDs                                 | 1 port, 2 IDs                                                                                    |

Table 5. FPGA Connections to Processor's DDR Memory Controller

The SoC FPGAs with an ARM Cortex-A9 processor also support ARM's AXI Exclusive feature—essentially, a special, hardware-based semaphore operation for a transaction, but without dedicating the bus to a particular master for the duration of the operation. AXI Exclusive semaphore-type operations do not impact bus access latency or the maximum achievable bandwidth. On Altera SoC FPGA devices, the AXI Exclusive feature supports transactions across all DDR memory ports. In other devices, the feature is only available on a port-by-port basis.

## **Hardware Acceleration and Cache Coherency**

One of the additional potential benefits of the integrated processor and FPGA system is the ability to boost system performance by accelerating compute-intensive functions in FPGA logic. The processor can be offloaded by accelerating practically anything in FPGA logic—from calculating a cyclic-redundancy check (CRC) to offloading the entire TCP/IP stack. When the FPGA-based accelerator produces a new result, the data needs to be passed back to the processor as quickly as possible, so that the processor can update its view of the data.

ARM Cortex-A9-based SoC FPGAs include a feature called an Accelerator Coherency Port (ACP). Through the ACP, new data produced by an FPGA-based hardware accelerator is transferred directly to the processor's L2 cache via a low-latency direct connection—not just quickly but coherently.

Because the ACP logic automatically maintains coherency, a coherent data transfer requires approximately 30 cycles. The alternative method to ensure data coherency is to flush the L2 cache, which requires hundreds of cycles to complete. As shown in Table 6, Altera SoC FPGAs support coherent transactions for both FPGA-based functions and for processor peripherals. Other SoC FPGAs only support FPGA functions via a single dedicated port and do not support transactions from processor peripherals.

ARM originally designed the ACP interfacefor full-custom system-on-chip devices, which generally have only a few dedicated accelerators or a few peripherals that require ACP support. Consequently, the ARM ACP interface only supports eight total transactions in flight or pending. However, because of the SoC FPGA's flexible and programmable architecture, there may be many more hardware accelerators that require coherent support. To support more than eight such functions, Altera SoC FPGAs incorporate an ACP ID mapper that supports an unlimited number of pending transactions with any eight transactions currently in flight.

|                                               | Altera SoC                 | Vendor B                     |

|-----------------------------------------------|----------------------------|------------------------------|

| FPGA-Based Masters Supported by ACP           | Yes                        | Yes                          |

| Processor Peripheral Masters Supported by ACP | Yes                        | No                           |

| ACP ID Mapper                                 | Yes                        | No                           |

| ACP In-Flight Transactions Supported          | 8                          | 8 total in flight or pending |

| ACP Pending Transactions Supported            | Unlimited                  | 8 total in flight or pending |

| ACP Port Configuration                        | x64 AXI                    | x64 AXI                      |

| ACP Port Clock Source                         | 1/2 CPU Clock<br>(400 MHz) | FPGA<br>(150 MHz)            |

Table 6. Accelerator Coherency Port Differences in SoC FPGAs

## Additional Memory Controllers Improve Maximum System Performance

SoC FPGAs all include a dedicated DDR hard memory controller as part of the processor subsystem, primarily to store and retrieve code and data for the processor. For cost-saving purposes, the processor's memory controller also can be shared with logic functions in the FPGA.

For maximum performance in some applications, however, it may be best to keep the processor's and FPGA's memory controllers separate, as outlined in Table 7. If the application software is particularly demanding, then the processor benefits from having its own exclusive memory array. Likewise, high-bandwidth FPGA applications also benefit from having their own exclusive memory arrays.

Table 7. Using Processor and FPGA Memory Interfaces for Various Application Types

| Application Type                                        | Processor Memory Controller                                                                                   | FPGA Memory Controller(s)                                                            |

|---------------------------------------------------------|---------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------|

| Lowest Cost                                             | Processor and FPGA functions share a common<br>DDR memory subsystem using processor's memory<br>controller    | Unused                                                                               |

| Processor and FPGA Share<br>Large Common Memory<br>Area | Processor and FPGA functions share a common<br>DDR memory subsystem using processor's memory<br>controller    | Available for other FPGA functions                                                   |

| Demanding Computational<br>System                       | Processor's memory controller dedicated to servicing the processor                                            | Any FPGA functions use FPGA memory<br>controller to offload HPS memory<br>controller |

| High-Bandwidth FPGA<br>Function                         | Processor uses processor's memory controller,<br>possibly shared with other lower-bandwidth FPGA<br>functions | FPGA exclusively uses FPGA memory controller(s)                                      |

As shown in Table 8, Altera's 28 nm SoC FPGAs also include one or three independent hard DDR memory controllers dedicated to FPGA logic functions, with the same sophisticated features and capabilities of the processor's memory controller. All the commercially-available SoC FPGAs support adding dedicated memory controllers in the FPGA fabric, built from programmable logic. The disadvantage is that these soft controllers compete for FPGA resources with other application logic. Constructing and closing timing on soft memory controllers also takes away valuable design time which could be spent developing more valuable proprietary IP.

Table 8. Dedicated Hard Memory Controllers and Soft Memory Controllers Exclusively for FPGA Applications

| Function/Feature                         | Altera SoC FPGA             | Vendor B             | Vendor C             |

|------------------------------------------|-----------------------------|----------------------|----------------------|

| Hard Memory Controller(s) in FPGA Fabric | 1 to 3, depending on device | Not available        | Not available        |

| Soft Memory Controller(s) in FPGA Fabric | Yes, uses FPGA logic        | Yes, uses FPGA logic | Yes, uses FPGA logic |

## System Reliability and Flexibility

Highly integrated SoC FPGAs also help create more reliable systems. Two important aspects help differentiate between the available SoC FPGA devices.

- How much memory protection is available in the system?

- How does the SoC FPGA respond to software bugs?

### Protecting Memory Contents with ECC

The need for detecting, correcting, and monitoring errors is a growing trend in designs today. As memory sizes and densities continue to increase, so does the need and importance for error checking and correction. Most modern systems include dedicated hardware to help ensure data integrity.

## **For more information, refer to the** *Error Correction Code in SoC FPGA-Based Memory Systems* white paper.

From an SoC FPGA perspective, this includes error correction code or ECC protection—not only as part of the memory controller, but also integrated within the processor's on-chip memories, caches, and peripheral buffers. ECC circuitry makes a system more robust and resilient against unexpected data errors or corrupted data.

While an immediate and essential reaction is to add ECC to the system main memory for applications where data integrity is critical, it is important that everything that can be protected is protected. In addition to main memory, it is also important to ensure that the L2 cache and on-chip RAM are also ECC protected. This is another area where architecture matters. A well-thought-out architecture considers every step in the data transfer path and includes appropriate protection at each step. Unless it is built into the device, ECC protection is incredibly difficult and expensive to add.

Table 9 summarizes the ECC circuitry implemented throughout the system.

#### Table 9. ECC in SoC FPGAs

|                                                                                                   | Altera SoC FPGA                                                                                               | Vendor B                                    |

|---------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------|---------------------------------------------|

| L1 Cache                                                                                          | Parity (part of Cortex-A9 implementation)                                                                     | Parity (part of Cortex-A9 implementation)   |

| L2 Cache                                                                                          | Yes                                                                                                           | No ECC                                      |

| External DDR Memory Controller<br>(Single Error Correction and Double Error<br>Detection <b>)</b> | x16<br>x32                                                                                                    | x16 only                                    |

| On-Chip RAM                                                                                       | Yes                                                                                                           | Parity, No ECC                              |

| Quad SPI Controller                                                                               | Yes                                                                                                           | No ECC                                      |

| NAND Controller                                                                                   | 512 byte ECC sector size<br>(4, 8, or 16 bit correction)<br>1,024 byte ECC sector size<br>(24 bit correction) | 1 bit hardware support with software assist |

| SD/MMC/SDIO Controller                                                                            | Yes                                                                                                           | No ECC                                      |

| DMA Controller                                                                                    | Yes                                                                                                           | No ECC                                      |

| 10/100/1G Ethernet Controller                                                                     | Yes                                                                                                           | No ECC                                      |

| USB 2.0 OTG Controller                                                                            | Yes                                                                                                           | No ECC                                      |

The L1 caches are integral parts of the ARM Cortex-A9 processor. For performance reasons and due to their smaller size, the L1 caches as implemented by ARM use parity to detect single-bit errors, but do not include full ECC.

Another area worth highlighting is the NAND flash. NAND flash is useful for file system storage, but somewhat less reliable than NOR flash. Therefore, ECC on the NAND flash is useful to eliminate errors. Earlier versions of NAND flash memory controllers include single-bit ECC protection. While this is of some benefit, the CPU must get involved for anything beyond that, which can result in a significant performance impact since the CPU must manage ECC in software. More modern NAND memory controllers include multi-bit ECC protection. Specifically, the NAND flash controller implemented in the Altera SoC FPGA includes 4, 8, and 16 bit correction for 512 byte sector sizes and 24 bit correction for 1,024 byte sector sizes. This provides greater, needed protection without diminishing performance.

#### Memory Protection for Shared Memory

Memory protection is a feature often associated with more advanced processors. Whether it is called a memory management unit (MMU) or memory protection unit (MPU), the processor's memory protection unit prevents errant or illegal processor transactions from reading or corrupting other memory regions. In the Cortex-A9 processor, ARM extends this protection concept with TrustZone<sup>®</sup> technology, which provides a system-wide approach for security-sensitive systems.

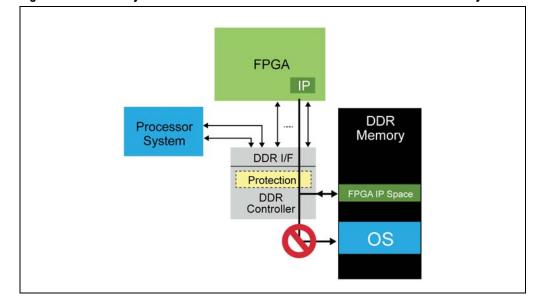

Some SoC FPGAs extend memory protection to the FPGA. Why is memory protection from or for the FPGA needed? The processor and FPGA can share a single external DDR memory interface in order to save cost, reduce board space, or save power. What if the custom FPGA logic accidentally overwrites a section of memory belonging to the processor's data, application code, or operating system (OS) kernel? This may cause a system fault or vector the processor off in the wrong direction.

To prevent this from happening, specific memory regions may be dedicated to the operating system and embedded software applications while other memory regions may be dedicated to FPGA-based functions, as shown in Figure 7. Via memory protection, the FPGA-based functions are prevented from corrupting the operating system or embedded software regions.

Figure 7. DDR Memory Protection Where Processors and FPGA Share a Common Memory

Memory Protection

Table 10 summarizes the memory protection for FPGA accesses to external memory.

| Function/Feature                  | Altera SoC FPGA                                       | Vendor B       |  |  |  |  |

|-----------------------------------|-------------------------------------------------------|----------------|--|--|--|--|

| TrustZone Security                | Yes                                                   | Yes            |  |  |  |  |

| TrustZone Region Size Granularity | 1 MB boundary                                         | 64 MB boundary |  |  |  |  |

|                                   | 20 user-definable protection rules. Each rule defines |                |  |  |  |  |

TrustZone Address range

Master ID range Port range (mask) Inclusive/exclusive

| Table 10. | Memory  | Protection   | for | FPGA | Accesses | to | External | Memory   |

|-----------|---------|--------------|-----|------|----------|----|----------|----------|

| 10NIC 10. | MICHIUI | 1 1010011011 |     | IIUA | AUUUJJUJ | ιu | External | MICHIULY |

Both SoC FPGAs support ARM's TrustZone security features; however, the Altera SoC FPGA protects regions with finer granularity, down to 1 MB. Furthermore, the Altera SoC FPGA supports 20 user-definable protection rules for a specific region. This allows finer tuning and more precise control, making it possible to prevent FPGA masters from accessing undesired regions.

TrustZone

## Watchdog Reset and Its Effect on FPGA Logic

Watchdog timers prevent errant software from disabling a system. If the processor crashes in previous-generation two-chip processor plus FPGA solutions, the FPGA continues to operate while the processor's watchdog timer resets the processor and the system recovers as gracefully as possible. A properly architected SoC FPGA supports the same "independent" behavior plus provides the option to reconfigure the FPGA, if desired. It should not, however, mandate the FPGA to reconfigure in all cases unless that is the desired behavior, as specified by the system designer. In many cases, it may be critical for the FPGA logic to continue to monitor and respond to external stimuli while the processor resets itself. Therefore, it is important to inspect how the FPGA reconfiguration is handled in this circumstance.

As shown in Table 11, the reset circuitry in Altera SoC FPGAs matches historical usage. The reset circuitry for the processor and FPGA operate independently, although both optionally communicate reset events to the other. The developer decides how the FPGA portion should respond to a CPU reset, either by simply resetting portions of the configured FPGA logic, by completely reconfiguring the FPGA, or by completely ignoring it. In the case of SoC FPGA Vendor B, the FPGA logic is always reconfigured when a CPU reset occurs.

| Function/Feature              | Altera SoC FPGA                                               | Vendor B                  |

|-------------------------------|---------------------------------------------------------------|---------------------------|

|                               | User defined:                                                 |                           |

| FPGA Response to CPU Reset    | Reset flip-flops in FPGA logic as specific in user design, or | FPGA ALWAYS reconfigured  |

| TT UA Nespulise to OF O Neset | Reconfigure the FPGA logic, or                                | TT GA ALWATS TECOTINgureu |

|                               | No response                                                   |                           |

Table 11. CPU Reset in SoC FPGAs

## **Fail-Safe Booting and Configuration**

Being fully-programmable, single-chip systems, SoC FPGAs must successfully boot the processor and configure the FPGA before becoming fully functional. SoC FPGAs provide a fail-safe recovery method in case of a boot or configuration failure—a crucial feature for systems that support remote, in-field system updates. As summarized in Table 12, SoC FPGAs provide "fail-safe" recovery should there be a physical defect during configuration. The SoC FPGA device automatically loads an alternative configuration image if a CRC error occurs either in the configuration header or in the configuration image itself.

Altera SoC FPGAs provide additional fail-safe recovery for other logical defects. After the Altera SoC FPGA successfully boots, the boot loader software sets a bit indicating a successful configuration. However, if the boot loader fails to set the bit, then a watchdog timer triggers a warm reset to restart the boot process. When the Altera SoC FPGAs restarts the boot process, the processor sees that the previous boot attempt failed and chooses the last known good image.

Table 12. Fail-Safe Processor Boot/FPGA Configuration in SoC FPGA Devices

| Function/Feature                         | Altera SoC FPGA | Vendor B |

|------------------------------------------|-----------------|----------|

| Fail-Safe Reboot on Physical Boot Defect | Yes             | Yes      |

| Fail-Safe Reboot on Logical Boot Defect  | Yes             | No       |

## Flexibility

Flexibility is a common reason that many designers use FPGAs in the first place. Fully-programmable SoCs simply extend design flexibility to the system level. This section highlights three architectural details to consider when choosing an SoC FPGA:

- Processor boot and FPGA configuration options

- On-chip FPGA interfaces

- Common package footprints

## **Multiple Options for Processor Boot and FPGA Configuration**

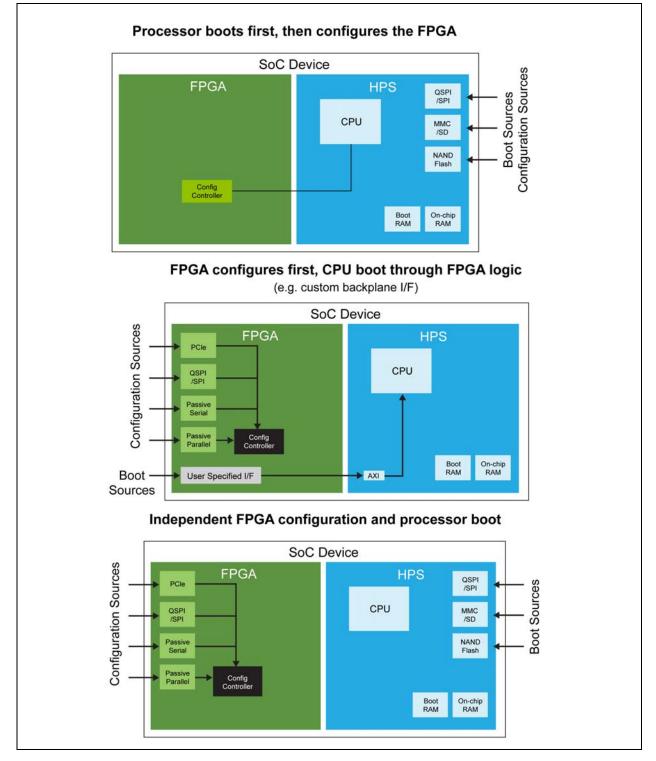

The need for flexibility begins at boot. There are three options in SoC FPGAs for booting the processor and configuring the FPGA as illustrated in Figure 8.

All SoC FPGAs support the processor-like "CPU first" method (Figure 8, top), where the processor boots first and then configures the FPGA under software control. This mode functions like a normal processor boot, except that the processor configures the FPGA as a big "peripheral" device. The advantage of this mode is that it adheres to the traditional approach of bringing up the processor first, and existing boot code may translate easily; possible disadvantages of this approach would be if the system has configuration time constraints that won't tolerate a delay while the processor boots or there are advantageous functions the FPGA can perform while the processor is still booting.

The second option (Figure 8, middle) has the FPGA configure first and then boots the CPU through FPGA logic. One use of this method could be to have the FPGA examine and secure the system before allowing the processor to boot, or various other secure boot modes. Another case would be to use the FPGA to bring up a custom backplane which could then be used to boot the processor.

The third option (Figure 8, bottom) is completely independent processor boot and FPGA configuration mechanisms. In this example, the processor boots from one of its flash memory sources. Independently, the FPGA configures from one of its data sources. Consequently, the FPGA subsystem can configure fast enough—in as little as 13 ms—to allow a PCI Express<sup>®</sup> (PCIe<sup>®</sup>) interface to configure the remainder of the FPGA.

Table 13. Processor Boot and FPGA Configuration Options in SoC FPGAs

| Function/Feature                                                  | Altera SoC FPGA | Vendor B |

|-------------------------------------------------------------------|-----------------|----------|

| CPU Boots First, CPU Configures FPGA                              | Yes             | Yes      |

| FPGA Configures First, CPU Boots through FPGA Fabric or Backplane | Yes             | No       |

| CPU Boots Independently and FPGA Configures Independently         | Yes             | No       |

Table 13 shows the different boot modes supported by two of the SoC FPGAs. Currently, the Altera SoC FPGA is the only ARM Cortex-A9 processor-based SoC FPGA that was designed to support all three of these options.

#### **Multiple Boot Images**

Many SoC developers prefer to store their boot images in quad SPI flash due to its inherent reliability (NOR technology), relatively low cost, and minimal I/O requirements. For systems in which the processor is responsible for configuring the FPGA, the flash boot image will contain both hardware and software content including:

- CPU boot code

- Operating system (OS)/real-time operating system (RTOS)

- Application code and data

- FPGA configuration

Frequently multiple "boot images" are desired: One to hold the factory default image and at least one to hold system updates. The factory default image is always stored in case the update fails to load properly. The system then automatically reverts back to a known good image and the update can be retried. Estimates for full boot images based on "minimal" and "substantial" software requirements, and hardware images for small, medium, and large FPGA densities are provided in Table 14.

For quad SPI devices, the amount of storage needed may be an issue depending on the SoC vendor selected. Altera provides a quad SPI interface that support up to a 4 GB address range, and up to four chip selects. Vendor B's quad SPI supports a 16 MB address range with up to two chips selects, limiting total boot image size to 32 MB.

| Software Requirements             |       | Minimal |       |       | Substantial |       |

|-----------------------------------|-------|---------|-------|-------|-------------|-------|

| User Space Code (MB)              | 5     | 5       | 5     | 50    | 50          | 50    |

| Linux Kernel (MB)                 | 3     | 3       | 3     | 5     | 5           | 5     |

| Boot Code (MB)                    | 0.5   | 0.5     | 0.5   | 0.5   | 0.5         | 0.5   |

| FPGA Density                      | Small | Medium  | Large | Small | Medium      | Large |

| FPGA HardwareImage (MB)           | 2.4   | 6.1     | 14.4  | 2.4   | 6.1         | 14.4  |

| Total Storage Required            |       |         |       |       |             |       |

| Single Image (MB)                 | 11    | 15      | 23    | 58    | 62          | 70    |

| Dual Image (MB)                   | 22    | 29      | 46    | 116   | 123         | 140   |

| Altera SoC FPGA                   |       |         |       |       |             |       |

| Single Image (# Quad SPI Devices) | 1     | 1       | 1     | 1     | 1           | 1     |

| Dual Image (# Quad SPI Devices)   | 1     | 1       | 1     | 1     | 1           | 2     |

| Vendor B                          |       |         |       |       |             |       |

| Single Image (# Quad SPI Devices) | 1     | 1       | 2     | N/A   | N/A         | N/A   |

| Dual Image (# Quad SPI Devices)   | 2     | 2       | N/A   | N/A   | N/A         | N/A   |

Table 14. Boot Image Size Requirements and Mapping to Quad SPI Devices

As shown by the table, Altera SoC FPGAs can support multiple large boot images. Vendor B's SoC FPGAs are limited in terms of the size and number of boot images they can handle. Estimates based on maximum quad SPI device size of 1 Gb (128 MB).

## **On-Chip FPGA Interfaces**

Flexibility also extends to on-chip FPGA interfaces. There are times when an application demands a feature-rich, standards-based interface; and times when something simple or customized is all that is needed.

For those applications that demand advanced features, SoC FPGAs use ARM's AXI to connect the processor, hard peripherals, and FPGA logic. The AXI standard provides a fast and wide interface using a proven industry standard. But what about the IP cores that don't need all the feature richness of AXI? What if scalability is more important? At one end of the spectrum a custom, 1000-wire interface may be what is needed; at the other end of the spectrum, a single wire may be needed to blink an LED or read a switch.

To address this need for variation, in addition to the AXI interface, the Altera SoC FPGAs support the Avalon® Memory-Mapped (Avalon-MM) interface and Avalon Streaming (Avalon-ST) interface. These scalable Altera interface standards offer the right fit for less demanding or other specific functions. This enables the IP designer to choose the optimum interface for each function. This also allows existing Altera FPGA customers to continue to use IP built on these interfaces without a forced migration to AXI for IP that would not benefit.

**\*** For more information about Avalon interfaces, refer to the *Avalon Interface* Specification.

Table 15 summarizes the FPGA IP interfaces.

#### Table 15. FPGA IP Interfaces Supported in SoC Devices

| Function/Feature   | Altera SoC<br>FPGA | Vendor B |

|--------------------|--------------------|----------|

|                    | AXI                |          |

| FPGA IP Interfaces | Avalon-MM          | AXI      |

|                    | Avalon-ST          |          |

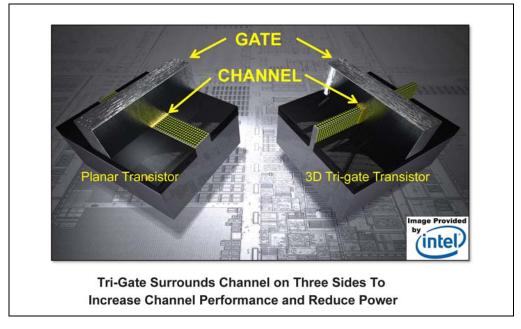

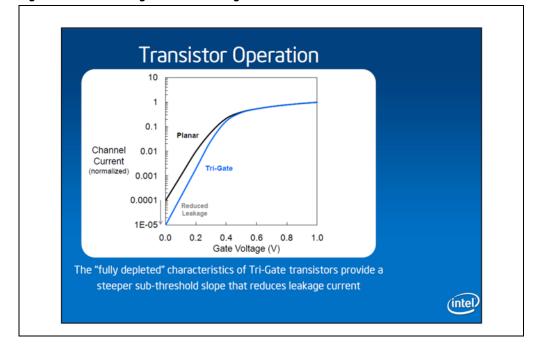

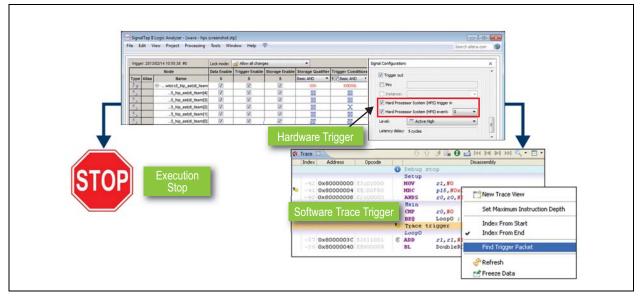

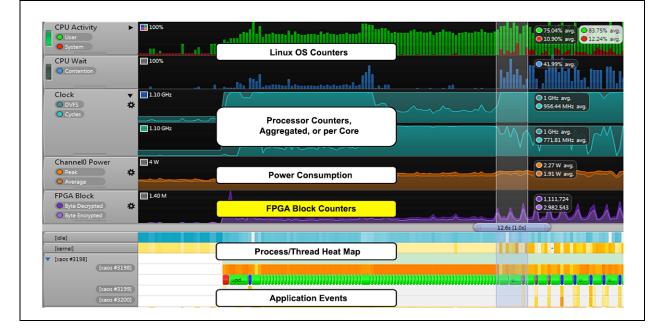

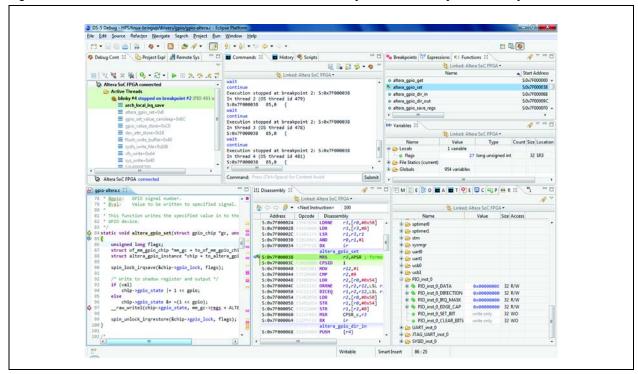

## **Common Footprint Density/Transceiver/Feature Migration**